简介

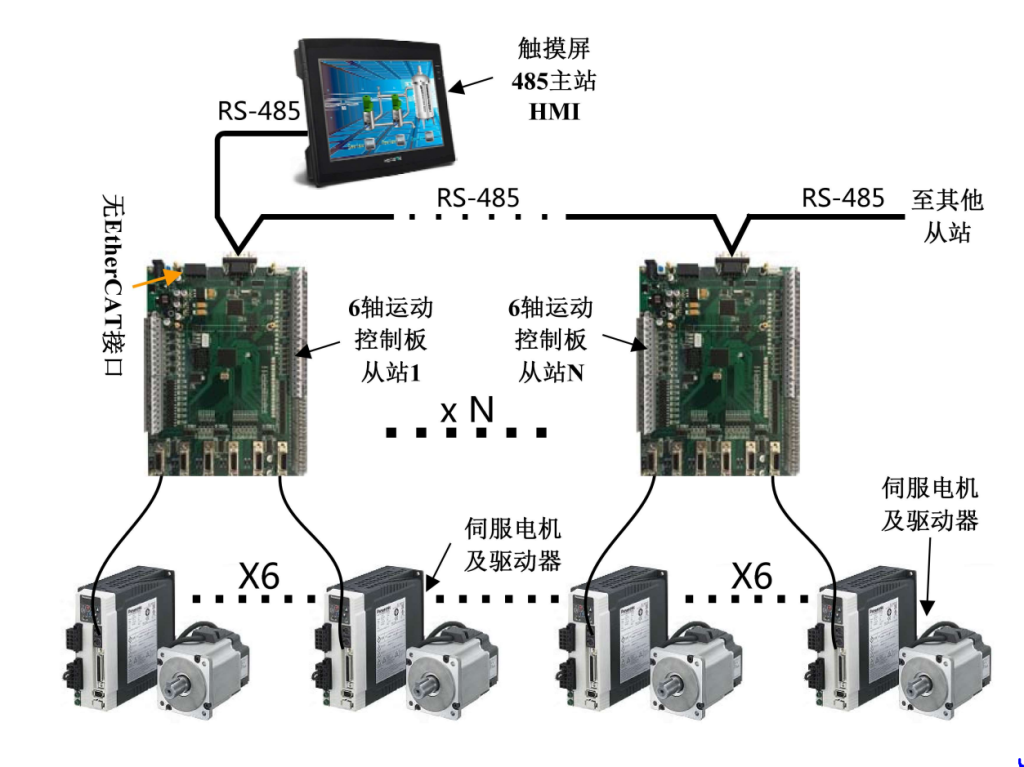

本系统采用与EtherCAT总线相同的一主多从结构,由一个EtherCAT主站和若干个从站组成,主站可选带标准以太网卡的PC,从站可以是通用I/O口从站、信号采集从站及驱动器

硬件设计

运动控制板:

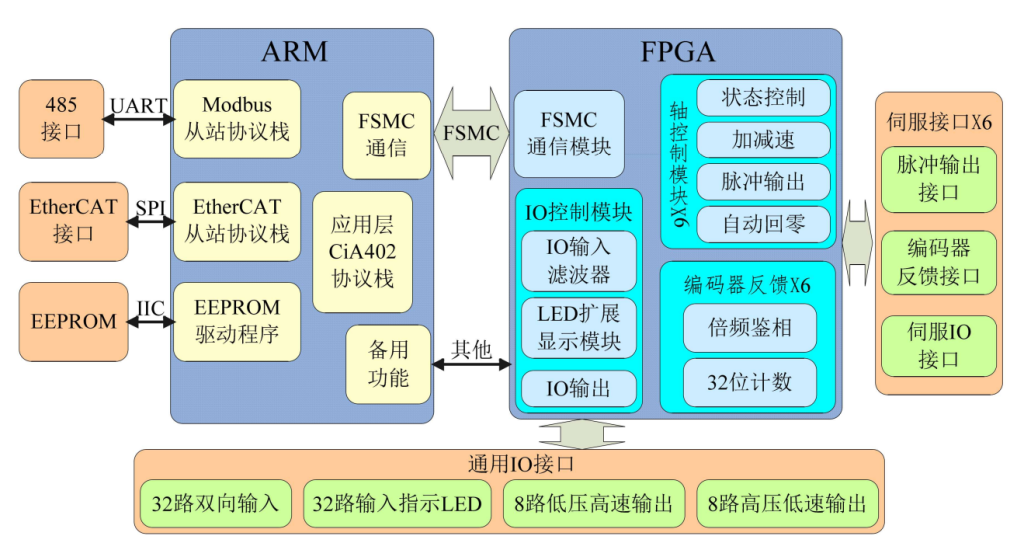

根据运动控制板的功能目标,设计如图的控制板架构,主控芯片采用ARM + FPGA的方案。ARM芯片作为主控器件,选型使用STM32F407VGT6,负责通过EtherCAT总线或RS485总线与上位机通信。FPGA主要完成运动控制、I/O控制及与ARM的通信任务,选型为Cyclone IV EP4C15F17C8.

EtherCAT从站通讯板:

要发挥出运动控制卡中ARM和FPGA的性能,两者之间高效的通信是必要的,在这里通信由EtherCAT通信板完成。通信板选用ET1100作为从站通信核心器件,实现EtherCAT网络的数据链路层功能。

系统软件

主站平台:

主站选用一块带DMA功能的通用网卡+PC构成,运行CoDeSys (Controlled Development System)商业主站软件。

EtherCAT从站软件:

EtherCAT从站程序包括了移植过来的EtherCAT从站协议栈和EtherCAT从站应用层CiA402程序